# Code Generation and Simulation of an Automatic, Flexible QC-LDPC Hardware Decoder

by

Mirko von Leipzig

Thesis presented in partial fulfilment of the requirements for the degree of Master of Science in Electronic Engineering in the Faculty of Engineering at Stellenbosch University

Department of Electrical & Electronic Engineering, Stellenbosch University, Private Bag X1, Matieland 7602, South Africa

Supervisor: Dr G-J van Rooyen

March 2015

## Declaration

By submitting this thesis electronically, I declare that the entirety of the work contained therein is my own, original work, that I am the sole author thereof (save to the extent explicitly otherwise stated), that reproduction and publication thereof by Stellenbosch University will not infringe any third party rights and that I have not previously in its entirety or in part submitted it for obtaining any qualification.

Date: ..... November 2014

Copyright © 2015 Stellenbosch University All rights reserved.

### Abstract

Iterative error correcting codes such as LDPC codes have become prominent in modern forward error correction systems. A particular subclass of LDPC codes known as quasicyclic LDPC codes has been incorporated in numerous high speed wireless communication and video broadcasting standards. These standards feature multiple codes with varying codeword lengths and code rates and require a high throughput. Flexible hardware that is capable of decoding multiple quasi-cyclic LDPC codes is therefore desirable.

This thesis investigates binary quasi-cyclic LDPC codes and designs a generic, flexible VHDL decoder. The decoder is further enhanced to automatically select the most likely decoder based on the initial *a posterior* probability of the parity-check equation syndromes.

A software system is developed that generates hardware code for such a decoder based on a small user specification. The system is extended to provide performance simulations for this generated decoder.

## Uitreksel

Iteratiewe foutkorreksiekodes soos LDPC-kodes word wyd gebruik in moderne voorwaartse foutkorreksiestelsels. 'n Subklas van LDPC-kodes, bekend as kwasisikliese LDPC-kodes, word in verskeie hoëspoed-kommunikasie- en video-uitsaaistelselstandaarde gebruik. Hierdie standaarde inkorporeer verskeie kodes van wisselende lengtes en kodetempos, en vereis hoë deurset. Buigsame apparatuur, wat die vermoë het om 'n verskeidenheid kwasisikliese LDPC-kodes te dekodeer, is gevolglik van belang.

Hierdie tesis ondersoek binêre kwasisikliese LDPC-kodes, en ontwerp 'n generiese, buigsame VHDL-dekodeerder. Die dekodeerder word verder verbeter om outomaties die mees waarskynlike dekodeerder te selekteer, gebaseer op die aanvanklike a posteriori-waarskynlikheid van die pariteitstoetsvergelykings se sindrome.

'n Programmatuurstelsel word ontwikkel wat die fermware-kode vir so 'n dekodeerder genereer, gebaseer op 'n beknopte gebruikerspesifikasie. Die stelsel word uitgebrei om werksverrigting te simuleer vir die gegenereerde dekodeerder.

## Acknowledgements

I would like to express my sincere gratitude to the following people:

- my parents, for their support, concern and motivation,

- my sister, for her company and constant niggling,

- Gert-Jan van Rooyen, for being a valuable bouncing board for my ideas,

- my friends, for their critique and distractions.

## Contents

| Declaration                                                                               | i                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Abstract                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Uitreksel                                                                                 | iii                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Acknowledg                                                                                | iv iv                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| List of Figu                                                                              | res vii                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| List of Code                                                                              | e Snippets x                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Nomenclatı                                                                                | ure xi                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| List of Abb                                                                               | reviations xiii                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 1.2 Moti<br>1.3 Obje<br>1.4 Cont                                                          | ground1vation for Work1ctives2ributions2is Overview3Existing Literature3System Overview4Hardware Decoder Design and Code Generation4                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 2.1 Digit<br>2.2 LDP<br>2.3 Itera<br>2.3.1<br>2.3.2<br>2.4 LDP<br>2.4.1<br>2.4.2<br>2.4.3 | C Decoding       15         LDPC Codes Message Formats       17         Parity-Check Message Approximations       19         LDPC Message Passing Algorithms       20         eral LDPC Encoding       21         Lookup Table       21         Triangular Parity-Check Matrix       21         Approximate Triangular Parity-Check Matrix       22         Block-Triangular parity-check Matrix       22 |  |  |  |  |  |  |  |

### Stellenbosch University https://scholar.sun.ac.za

|            | $2.6 \\ 2.7$      | Quasi-cyclic LDPC codes       LDPC Code Detection | $\frac{26}{28}$ |  |  |  |  |  |  |

|------------|-------------------|---------------------------------------------------|-----------------|--|--|--|--|--|--|

| 3          | Syst              | stem Design 29                                    |                 |  |  |  |  |  |  |

|            | 3.1               | Decoder Concept                                   | 30              |  |  |  |  |  |  |

|            | 3.2               | Simulation Subsystem                              | 31              |  |  |  |  |  |  |

|            | 3.3               | Code Generation Subsystem                         | 32              |  |  |  |  |  |  |

| 4          | Har               | rdware Design                                     | 34              |  |  |  |  |  |  |

|            | 4.1               | Clock Synchronisation                             | 34              |  |  |  |  |  |  |

|            | 4.2               | Message Format                                    | 34              |  |  |  |  |  |  |

|            | 4.3               | Transcendental Functions                          | 35              |  |  |  |  |  |  |

|            | 4.4               | Fixed Point versus Floating Point                 | 35              |  |  |  |  |  |  |

|            | 4.5               | Sign Magnitude versus Two's Complement Format     | 35              |  |  |  |  |  |  |

|            | 4.6               | Message Passing Schedule                          | 35              |  |  |  |  |  |  |

|            | 4.7               | Decoder Design                                    | 36              |  |  |  |  |  |  |

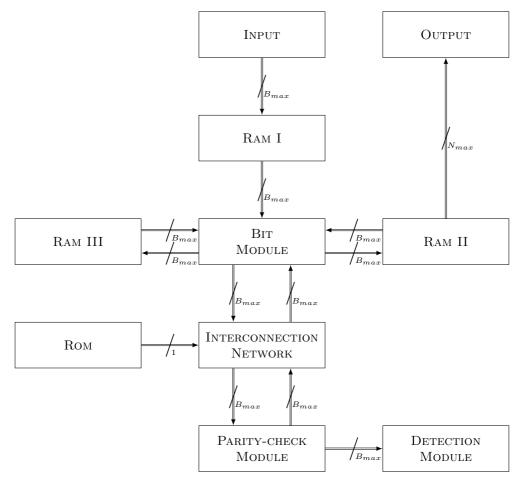

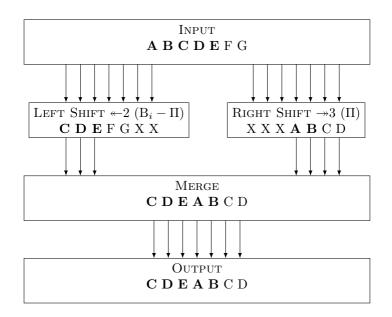

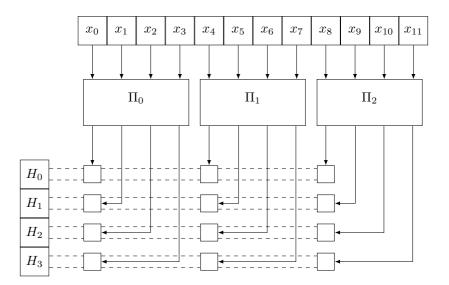

|            |                   | 4.7.1 Interconnection Network                     | 37              |  |  |  |  |  |  |

|            |                   | 4.7.2 Bit Module                                  | 41              |  |  |  |  |  |  |

|            |                   | 4.7.3 RAM                                         | 43              |  |  |  |  |  |  |

|            |                   | 4.7.4 ROM                                         | 45              |  |  |  |  |  |  |

|            |                   | 4.7.5 Parity-check Module                         | 45              |  |  |  |  |  |  |

|            |                   | 4.7.6 Detection Module                            | 46              |  |  |  |  |  |  |

|            |                   | 4.7.7 Control Module                              | 48              |  |  |  |  |  |  |

|            |                   | 4.7.8 Timing Overview                             | 49              |  |  |  |  |  |  |

| 5          | Soft              | ware Design                                       | 52              |  |  |  |  |  |  |

| 0          | 5.1               | Code Generation Subsystem                         | 53              |  |  |  |  |  |  |

|            | 5.2               | Simulation Subsystem                              | 55              |  |  |  |  |  |  |

|            | 5.3               | Test Environment                                  | 59              |  |  |  |  |  |  |

| 6          | Sim               | ulation Results                                   | 62              |  |  |  |  |  |  |

| 5          |                   |                                                   | -               |  |  |  |  |  |  |

| 7          | Con               | nclusion                                          | 68              |  |  |  |  |  |  |

| Δ          | A IEEE 802.11n 70 |                                                   |                 |  |  |  |  |  |  |

| 1 <b>I</b> |                   |                                                   |                 |  |  |  |  |  |  |

$\mathbf{vi}$

## List of Figures

| 2.1  | A basic communications system                                     |

|------|-------------------------------------------------------------------|

| 2.2  | General APP factor graph                                          |

| 2.3  | APP example factor graph                                          |

| 2.4  | APP example: step 1                                               |

| 2.5  | APP example: step 2                                               |

| 2.6  | APP example: step 3                                               |

| 2.7  | APP example: step 4                                               |

| 2.8  | APP example: step 5                                               |

| 2.9  | APP example: final calculations at variable nodes                 |

| 2.10 | A Tanner graph and its parity matrix                              |

|      | Parity matrix in upper-triangular form                            |

| 2.12 | Parity matrix in approximate upper-triangular form                |

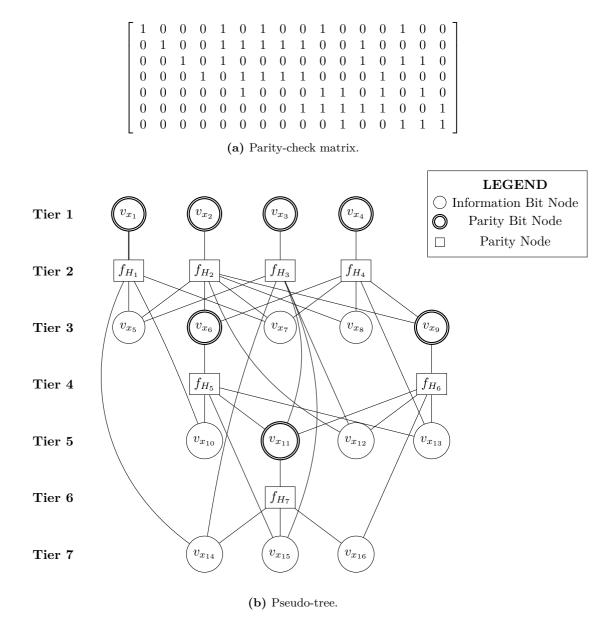

| 2.13 | A parity-check matrix and its pseudo-tree                         |

| 2.14 | A stopping set graph and its parity matrix                        |

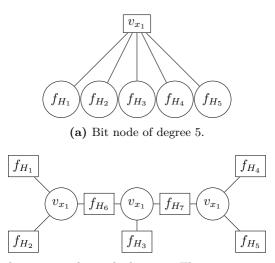

| 2.15 | Bit node degree reduction                                         |

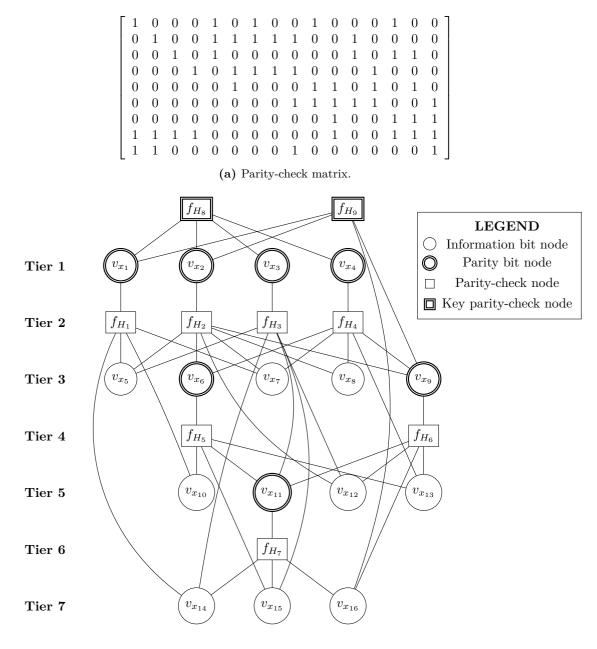

|      | QC-LDPC code example and its layered decoding Tanner graph        |

|      |                                                                   |

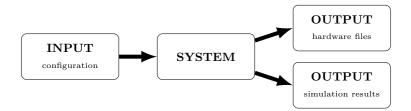

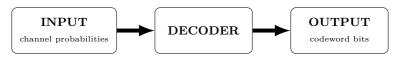

| 3.1  | Black box system overview                                         |

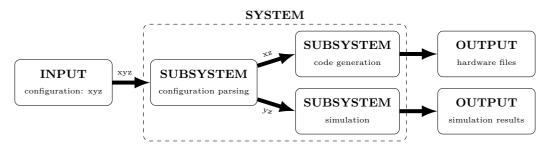

| 3.2  | Configuration parsing                                             |

| 3.3  | Decoding process                                                  |

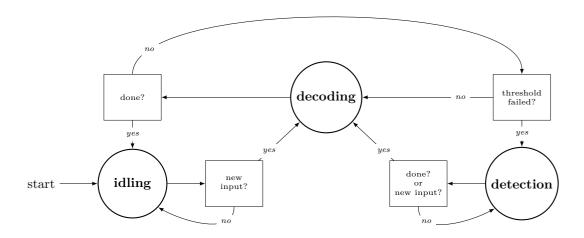

| 3.4  | Decoder state machine                                             |

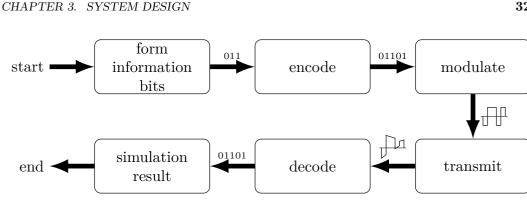

| 3.5  | Simulated communications process                                  |

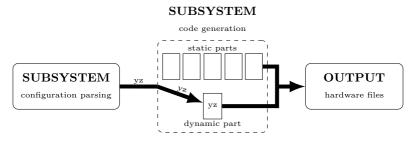

| 3.6  | Code generation subsystem                                         |

| 4 1  |                                                                   |

| 4.1  | Decoder module connections                                        |

| 4.2  | Barrel rotation to the right                                      |

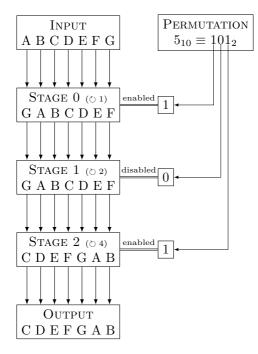

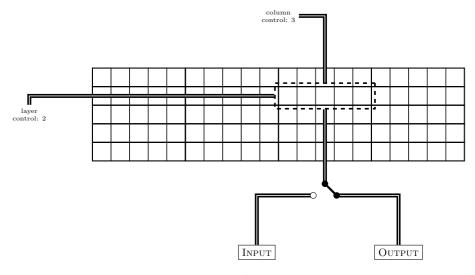

| 4.3  | QSN example                                                       |

| 4.4  | A parallel interconnection network                                |

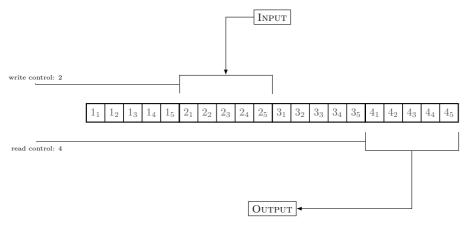

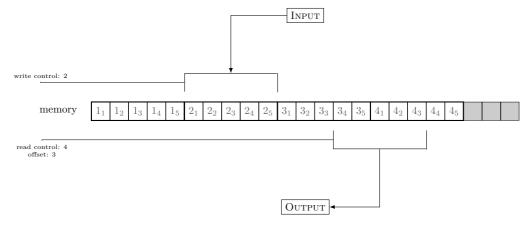

| 4.5  | RAM II model                                                      |

| 4.6  | RAM III model                                                     |

| 4.7  | RAM I model                                                       |

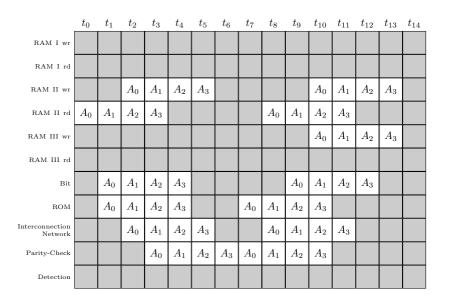

| 4.8  | Iteration zero timing diagram                                     |

| 4.9  | Initial-pass timing diagram                                       |

| 4.10 | Secondary-pass timing diagram                                     |

| 4.11 | Detection mode timing diagram                                     |

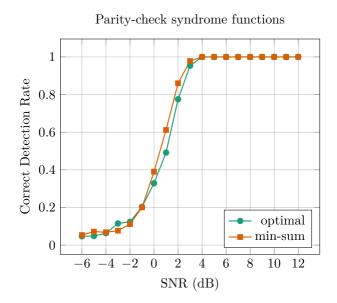

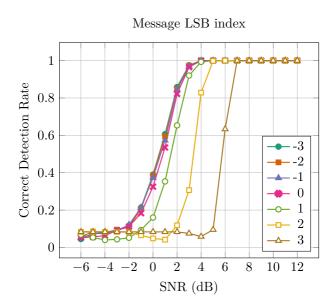

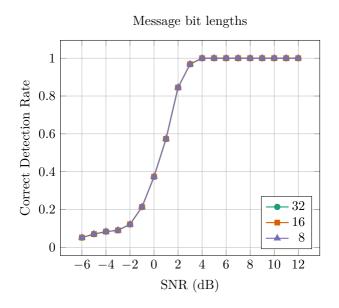

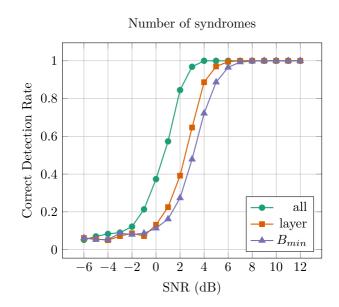

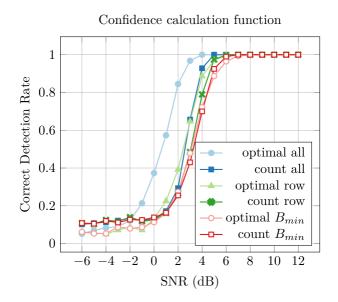

| 6.1  | Comparison of parity-check syndrome functions                     |

| 6.2  | Comparison of message LSB indices                                 |

| 6.3  | Comparison of message bib indices                                 |

| 6.4  | Comparison of number of parity-check syndromes used for detection |

| 6.5  | Comparison of detection algorithms                                |

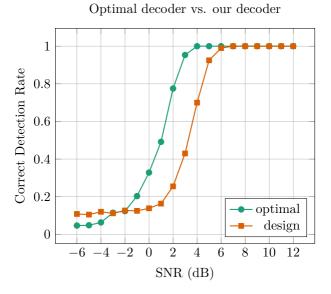

| 6.6  | Comparison of the optimal decoder and our design                  |

| -    |                                                                   |

| LIST | OF | FIG | URES |

|------|----|-----|------|

|------|----|-----|------|

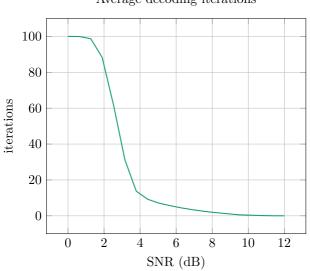

| 6.7  | Average decoding iter |         |          |          |   |       |   |       |   |       |   |       |   |       |   |   |       |    |

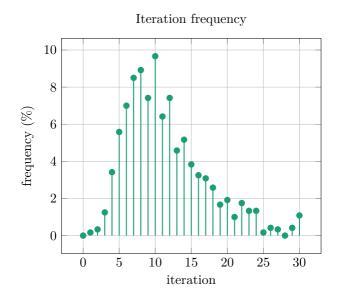

|------|-----------------------|---------|----------|----------|---|-------|---|-------|---|-------|---|-------|---|-------|---|---|-------|----|

| 6.8  | Average decoding iter |         |          |          |   |       |   |       |   |       |   |       |   |       |   |   |       |    |

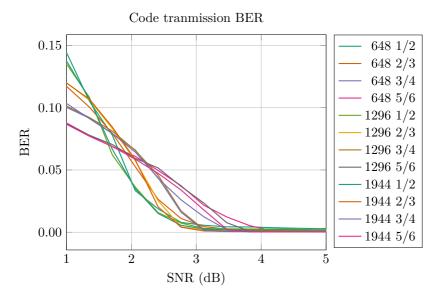

| 6.9  | IEEE 802.11n codes'   | BER.    |          |          | • | <br>• | • | • | <br>• | 67 |

| A.1  | IEEE 802.11n code cl  | naracte | eristic  | s        |   |       |   |       |   |       |   |       |   | <br>  |   |   |       | 70 |

| A.2  | Permutation Matrix:   | IEEE    | $648\ 1$ | /2       |   | <br>• |   |       |   | <br>• |   |       | • | <br>• | • |   |       | 71 |

| A.3  | Permutation Matrix:   | IEEE    | 648 2    | <i>'</i> |   |       |   |       |   |       |   |       |   |       |   |   |       |    |

| A.4  | Permutation Matrix:   | IEEE    | 648 3    | /4       |   | <br>• |   |       |   | <br>• |   |       | • | <br>• |   |   |       | 71 |

| A.5  | Permutation Matrix:   | IEEE    | 648 5    | /6       |   | <br>• |   |       |   | <br>• |   |       | • | <br>• |   |   |       | 71 |

|      | Permutation Matrix:   |         |          | '        |   |       |   |       |   |       |   |       |   |       |   |   |       | 72 |

|      | Permutation Matrix:   |         |          |          |   |       |   |       |   |       |   |       |   |       |   |   |       |    |

|      | Permutation Matrix:   |         |          |          |   |       |   |       |   |       |   |       |   |       |   |   |       |    |

| A.9  | Permutation Matrix:   | IEEE    | 1296     | 5/6      |   | <br>• |   |       |   | <br>• |   |       | • | <br>• |   |   |       | 72 |

|      | Permutation Matrix:   |         |          |          |   |       |   |       |   |       |   |       |   |       |   |   |       |    |

|      | Permutation Matrix:   |         |          |          |   |       |   |       |   |       |   |       |   |       |   |   |       |    |

|      | Permutation Matrix:   |         |          |          |   |       |   |       |   |       |   |       |   |       |   |   |       |    |

| A.13 | Permutation Matrix:   | IEEE    | 1944     | 5/6      |   | <br>• | • | <br>• |   | <br>• |   |       | • | <br>• | • | • |       | 73 |

## List of Algorithms

| 1 | QSN rotate right algorithm.                              | 39 |

|---|----------------------------------------------------------|----|

| 2 | Bit node sending algorithm.                              | 42 |

| 3 | Bit node receiving algorithm.                            | 43 |

| 4 | Parity-check unit execution for a single layer of a code | 47 |

| 5 | Detection module using the parity-check syndromes        | 48 |

## List of Code Snippets

| 5.1 | XML code set file.                                   | 52 |

|-----|------------------------------------------------------|----|

| 5.2 | XML block size, permutation matrix code description. | 53 |

| 5.3 | XML block size, matrix file code description.        | 53 |

| 5.4 | XML built-in code description.                       | 53 |

| 5.5 | Go Programming Language function definition.         | 55 |

| 5.6 | Go Programming Language interface example            | 56 |

| 5.7 | Encoding and transmission function prototypes        | 57 |

| 5.8 | Simulation configurations.                           | 57 |

| 5.9 | Higher order function example                        | 58 |

## Nomenclature

#### Vectors and Matrices

- **x** Row vector

- $\mathbf{x}^T$  Column vector

- $x_i$  Element *i* of vector **x**

- X Matrix

- $X_{i,j}$  Element in row *i*, column *j* of matrix **X**

#### Messages and Nodes

- $v_i$  Variable node i

- $f_j$  Function node j

- $Q_{i-j}$  Message from some node *i* to node *j*

- $Q_{i-j}^0$  Message containing the probability of a bit being zero

- $Q_{i-j}^1$  Message containing the probability of a bit being one

- $Q_{i-j}^{\mathrm{D}}$  Message containing the probabilities of a bit being zero or one as a tuple

- $Q_{i-j}^{LR}$  Message containing the likelihood ratio of a bit

- $Q_{i-j}^{\text{LLR}}$  Message containing the log-likelihood ratio of a bit

#### Variables

- $E_b$  Energy per bit

- $\eta$  Normalising constant

- $\varepsilon$  Binary symmetric channel crossover probability

- n Codeword length i.e. number of bits

- m Number of parity equations i.e. number of parity bits

- $n^b$  Quasi-cyclic LDPC parity matrix block columns

- $m^b$  Quasi-cyclic LDPC parity matrix block rows

- B Block size

- Π Quasi-cyclic LDPC permutation value

#### NOMENCLATURE

- $\Pi$  Quasi-cyclic LDPC permutation matrix

- G Global function

- $G_i$  Marginal function *i* of global function *G*

- g Local factor function of global function G

- $\sigma \qquad {\rm Transmission \ medium}$

- C A code

- $\gamma$  Characteristic function

- $\alpha$  Key parity-check node used in stopping-set encoding

- $\beta$  Key parity bit node used in stopping-set encoding

- $\Gamma_{\theta}$  Average syndrome log-likelihood of code  $C_{\theta}$

#### Operators

- $\overset{\sim i}{\underset{j}{\square}}$  Perform operation  $\square$  over all valid values of j excluding i

- $\oplus$  Logical XOR operation

- In Natural logarithm function

- e Natural exponent

- sgn Signum function

- L(x) Log-likelihood of x

## List of Abbreviations

| APP                  | a posteriori probability              |

|----------------------|---------------------------------------|

| BER                  | bit error rate                        |

| BPSK                 | binary phase-shift key                |

| FEC                  | forward error correction              |

| $\operatorname{GPL}$ | Go Programming Language               |

| IP                   | intellectual property                 |

| LDPC                 | low-density parity-check              |

| LLR                  | log-likelihood ratio                  |

| $\mathbf{LSB}$       | least significant bit                 |

| QC-LDPC              | quasi-cyclic low-density parity-check |

| RAM                  | random-access memory                  |

| ROM                  | read-only memory                      |

| SPA                  | sum-product algorithm                 |

| SNR                  | signal-to-noise ratio                 |

| VHDL                 | VHSIC Hardware Description Language   |

| XML                  | Extensible Markup Language            |

### Chapter 1

### Introduction

In recent years low-density parity-check (LDPC) codes have been included in multiple communications standards [1]. These standards usually include multiple LDPC codes with different code rates [1]. In this thesis a hardware decoding system capable of supporting an arbitrary set of binary, structured LDPC codes is developed. The decoder can support codes of different rates as well as different block sizes. The decoder is further developed to automatically select and decode the most likely code of the set. Applications of this technology include cognitive radio receivers and systems in which the encoder and decoder have no means to communicate a change in code.

#### 1.1 Background

Modern digital communications systems need to communicate information across noisy mediums or channels [2]. This is usually achieved by encoding the information bits into codeword bits at the sender. The encoding process adds redundant data to the information data according to some deterministic algorithm [2], which in turn allows the receiver to correct errors in the received data. This error correction can be achieved according to one of two general methodologies. The automatic repeat request methodology detects errors in the received data and requests a retransmission of the data if any are found [2]. The forward error correction (FEC) methodology uses the redundant data to correct errors, if any, in the received data without requiring retransmission [2].

The Shannon capacity of a channel is the upper bound on the rate of information transfer for a given channel bandwidth and signal-to-noise (SNR) power ratio with an arbitrarily small error probability [3]. In the 1990s, a family of FEC codes known as Turbo codes were discovered [3]. Turbo codes were the first codes capable of nearing the Shannon capacity of a channel. Prior to their discovery, it was believed that gains in channel capacity required increasing decoding complexity [3]. Turbo codes disproved this belief and consequently became widely adopted [2]. This led to vigorous investigation of other, similar codes. One such code family are the LDPC codes [3]. These LDPC codes are named for their sparse parity-check matrix.

#### 1.2 Motivation for Work

LDPC codes have shown similar error correcting performance to Turbo codes at high codeword lengths and rates [3]. They have been incorporated into numerous communication's standards, particularly in the high-speed video broadcast and wireless communications areas [1]. LDPC decoding complexity is linear with respect to codeword length while encoding is quadratic [4]. The long codeword length and high bit rate requirements of most stand-

#### CHAPTER 1. INTRODUCTION

ards incorporating LDPC codes cause both encoding and decoding speed to be issues in most designs [1]. LDPC codes are therefore often structured to help speed up encoding and decoding [1] such that both encoding and decoding of these structured codes is inherently parallel. Decoders for structured codes are therefore typically built on custom hardware [1] in order to meet the stringent speed requirements.

LDPC codes exist mainly as binary codes, however q-ary LDPC codes can and have been constructed. This thesis focuses exclusively on binary codes, however similar concepts could be used to incorporate q-ary codes.

Most standards specify multiple LDPC codes within a single standard [1], including codes of different codeword lengths and code rates. This calls for flexible hardware decoders capable of decoding any of the codes specified by a standard [1]. It would be beneficial if such a decoder design could easily be adapted to different standards without much effort. A system that generates code based on some user configuration solves this need. Compiling, synthesising and testing large hardware designs is time consuming [5]. It is therefore of use to have a means of simulating the performance of the hardware decoder prior to the implementation thereof, to allow the user to make configuration tweaks to better meet the expectations.

This work investigates binary LDPC codes and the design of an autonomous, flexible decoder capable of decoding a set of structured LDPC codes, as well as a code generation system that generates hardware code for such a decoder. A simulation package is also developed to simulate the performance of the decoder.

#### 1.3 Objectives

The objectives of this thesis are to

- design a flexible hardware decoder for arbitrary, structured LDPC codes,

- automate the decoder in so far as possible,

- design software to generate the hardware code for such a decoder based on user configuration,

- simulate such a decoder's performance.

#### 1.4 Contributions

This thesis makes the following contributions.

- We investigate and compile a wide range of existing LDPC decoding and encoding techniques.

- We investigate the proposed technique of Xia et al. [6] which allows us to find the most likely code of a set based on the received codeword. We show that this technique can be exploited at minimal extra cost to allow our decoder to autonomously select the correct code during the decoding process.

- We develop a software tool capable of generating code for a hardware decoder based on user configuration.

- We also develop a software model of the hardware decoder. This, coupled with software models of the communications system, allows us to simulate the performance of a decoder under certain channel and modulation conditions. This gives feedback to

#### 1.5 Thesis Overview

During the investigation of LDPC codes a number of topics were covered. An overview of the main points is covered here.

#### 1.5.1 Existing Literature

FEC codes, prior to the emergence of Turbo codes in 1993, used non-iterative decoding algorithms i.e. the codeword bits obtained their final, correct values after a single execution of the relevant decoding algorithm [3]. Turbo codes and other modern codes, including LDPC codes, utilise an iterative decoding process. In the iterative decoding process, the codeword bits undergo multiple iterations of updating their values.

The sum-product algorithm (SPA) [7] generalises algorithms commonly used in the artificial intelligence, digital communications and signal processing communities such as the Viterbi algorithm, the forward/backward algorithm and the Kalman filter [7]. In sections 2.3.1 and 2.3.2 the SPA is covered and use it to establish a link between iterative and non-iterative codes. The SPA operates on a graph created by factorising a complicated global function into the product of simpler factor functions [7]. In non-iterative codes, this graph is cycle free and the SPA gives an exact result. In iterative codes, the graph contains cycles and the SPA gives only an approximate result. The SPA is therefore executed iteratively on graphs with cycles in order to achieve a better approximation.

In section 2.4 we cover the derivation of the iterative LDPC decoding algorithm from the SPA. We start with the general *a posteriori* probability (APP) equation and show how this leads to the general iterative LDPC decoding algorithm.

Various approaches to lessening the computational load of the decoding process are discussed in sections 2.4.1 and 2.4.2. This includes numerical approximations, probability and likelihood formats, as well as likelihood update schedules.

LDPC encoding has a quadratic encoding complexity with respect to codeword length [4]. This is a problem because LDPC codeword length needs to be large in order to achieve good performance [8]. Several general approaches exist to deal with this issue, some of which are covered in section 2.5. In general, these approaches require a specific code structure. Two of the more promising approaches which can be applied to arbitrary LDPC codes, and guarantee linear encoding performance, are also covered.

Quasi-cyclic LDPC (QC-LDPC) codes are a structured subset of LDPC codes. A QC-LDPC code's parity matrix can be divided into equally sized blocks. Each block is either the zero matrix, or a shifted identity matrix. This builds an inherent parallel capability into the code as each bit and parity equation will feature at most once in a block. Furthermore, each block can be represented using a simple rotation module. This is useful for simplifying the connection system, which is usually the largest consumer of hardware real estate in a hardware implementation [1]. QC-LDPC codes are covered in more detail in section 2.6.

Standards implementing QC-LDPC codes usually define multiple such codes, with multiple different code rates and block sizes. It therefore becomes important to have flexible decoders capable of supporting variable code rates and block sizes. It may also be beneficial to have autonomous decoders, capable of detecting a change of code at the encoder. Xia et al. [6]

#### CHAPTER 1. INTRODUCTION

suggest using the average syndrome APP to select the most likely LDPC code from a set of predefined codes. This technique is fully explained in section 2.7.

#### 1.5.2 System Overview

The aim of this project is to create a software tool concerned with the code generation and performance simulation of a hardware QC-LDPC decoder.

The developed tool is split into two distinct systems: the hardware code generation system and the simulation system.

The code generation system takes a set of QC-LDPC code descriptions as input. These are used to generate various files containing the hardware decoder code. These files can then be compiled and synthesised into a working decoder and run on some target hardware system.

The simulation system likewise requires a set of QC-LDPC codes as input. It uses this code set to simulate various decoder performance properties such as the bit error rate and code misidentification rate across a range of SNR values. This is detailed fully in section 3

#### 1.5.3 Hardware Decoder Design and Code Generation

A simple hardware decoder is developed in section 4. It is capable of supporting multiple codes, with different code rates and block sizes. In doing so, we investigate multiple techniques to reduce the area and increase the speed of the decoder, particularly in the inter-routing network of the decoder, which typically consumes the most resources [1].

We further extend the design by incorporating the technique of Xia et al. [6] at minimal speed loss. This allows the decoder to decide which code of the set is the most likely to be active currently. This lets our decoder design become fully autonomous.

The developed software tool takes a set of QC-LDPC codes, and other user options (e.g. maximum iterations), and outputs hardware code files which can be compiled into the autonomous, flexible decoder. This decoder is then specific to the set of QC-LDPC codes. This tool is elaborated on in section 5.1.

#### 1.5.4 Simulation System

The simulation tool is discussed in section 5.2. It allows the user to specify channel and modulation conditions in addition to the decoder configuration. These are used to provide meaningful feedback to the user about the decoder's expected performance under these conditions. The feedback is provided by means of graphs and includes average bit error rate, average code misidentification rate, as well as bit error and code misidentification rates for each code.

The overall simulation system inputs are designed to be abstract. In our simulations, we implement only Gaussian noise channel models. The abstract nature of the system makes it very easy to add a new channel and other parameter models pertinent to the simulations.

### Chapter 2

### Literature Review

In this chapter we discuss existing literature pertaining to LDPC codes. We cover the early history of error correction in digital communications and how this led to the development and rise of iterative codes such as LDPC codes. The SPA is explained in section 2.3. We present a simple step-by-step example applying the SPA and show how the LDPC decoding algorithm can be derived from the general SPA. We link iterative and non-iterative codes using the SPA as a common starting point. In section 2.4 we derive common LDPC decoding algorithm approximations and discuss the implications of number formats on decoding complexity. Section 2.5 discusses various attempts at gaining linear encoding complexity, including two methods that manage to guarantee linear complexity for arbitrary LDPC codes. We then focus on structured LDPC codes, called QC-LDPC codes, which are commonly implemented [1]. Finally, we discuss a method proposed in [6], that allows for selecting the most likely code of a set for a received codeword.

#### 2.1 Digital Communications and Error Correction History

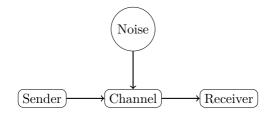

A basic communication system requires a sender, a receiver and a means to transport the information from the former to the latter. This transportation medium is commonly known as a channel [3]. The information may become distorted during transport due to interference on the channel. This distortion is usually called noise [3]. Figure 2.1 shows this basic communications system.

Originally, telecommunications systems used analogue signals to convey information [3]. These analogue signals become distorted prior to arriving at the receiver. At the receiver, a signal estimator uses the received noisy signal to provide an approximation of the original signal [3]. Analogue signals, by definition, allow for an infinite variation of possible values. This means that the receiver is never certain of the accuracy of the approximation.

The rise of digital communications over analogue started with the work of Nyquist in 1928 [3]. Nyquist proved that a band-limited signal can be perfectly reconstructed from a finite

Figure 2.1 – A basic communications system.

set of discrete-time samples of the signal [3]. In 1948 Shannon built on this by proving that these discrete samples could be represented by a finite number of amplitudes [3], dependent on the noise level. Combined, Nyquist and Shannon's work imply that any band-limited signal can be completely described by a finite set of discrete-time digital values even in the presence of noise. This led to the development of digital communications systems.

In a digital system, information needs to be in digital format before it can be sent. In a binary digital system this may require converting the information to a series of 1's and 0's called bits. These bits then get mapped to waveforms which can be transmitted across the channel [2]. This process is called modulation. A simple example is binary phase-shift key (BPSK) modulation. In BPSK a 1 is mapped to  $+E_b$  and a 0 to  $-E_b$ , where  $E_b$  is the bit energy [2]. Prior to the development of error correction codes, these modulation schemes were the only way of combating the errors caused by noise [3]. At the receiver, a demodulator takes the received, distorted waveform and makes a hard decision about the bit's value, based on whether a 1 or 0 is more likely. In the case of BPSK a demodulator would map any received waveform above zero to a 1, and below to a 0. An error would therefore occur if noise distorted the waveform to flip around the zero mark. The rate of these errors is directly correlated to the signal-to-noise power ratio (SNR) [2]. As the noise power cannot be controlled, it was believed that only by increasing waveform power,  $E_b$ , could one improve error performance [3].

Error correction coding started with another of Shannon's works, namely his famous channel capacity theorem [3]. Shannon proved that arbitrarily small error rates can be achieved for a noisy channel, as long as the bit transmission rate is lower than the channel's capacity [3]. This capacity is often called the Shannon capacity of a channel [2]. Shannon's work proved that smart encoding and decoding of digital signals could drastically improve a communications system's performance without requiring an increase in power [3]. Unfortunately, the proof does not include information on how these codes should be structured to achieve this [3].

The earliest codes could only perform error checking i.e. they could only detect whether or not an error had occurred. A simple example of such a code is the parity bit. In a parity bit code, a single bit is added to the information bits. This bit is called the parity bit and together with the information bits forms the codeword. The parity bit is used to ensure that the codeword as a whole has either an odd number of 1's (odd parity) or an even number of 1's (even parity) – the choice of which parity is arbitrary. This allows the receiver to detect if an odd number of errors occurred as the parity of the codeword would be incorrect.

Hamming and Golay were the first to develop error codes capable of detecting and correcting errors [3]. Hamming codes function by having multiple parity bits mixed in between the information bits. The parity bits are positioned such that, if the bits are indexed starting from 1, they cover every index number whose binary representation contains only a single 1 [2]. The parity bits values are further only calculated using a subset of the codeword bits. A parity bit covers all the bits whose index yield a non-zero result when logically AND'ed with the parity bit's index [2]. Error's in the parity bits are detected as usual – if the overall parity is incorrect, an error has occurred. When an error is detected, adding the positions of all the parity bits that indicated an error will result in the position of the erroneous bit [2]. Hamming codes therefore allow the detection and correction of a single bit error.

Early error correction decoders, such as for the Hamming and Golay codes, exclusively used the hard decision bit outputs of a demodulator. Modern codes often utilise soft-decision decoding which skips the demodulator completely [3]. Each bit is attributed a probability for being a 1 or a 0 based on the received waveform and the channel model. The entire codeword is then analysed using each bit's probabilities to find the most likely codeword [2]. Examples of such codes are the Viterbi codes, convolutional codes and includes iterative codes, such as the LDPC codes we are focussing on.

The driving goal for the field of error correction has always been to get as close as possible to the Shannon capacity of a channel [3]. This would allow for the highest efficiency in terms of bandwidth and power used for effective bit rate [3]. The discovery and adoption of iterative codes such as Turbo and LDPC codes have dramatically narrowed the gap to the Shannon capacity [3].

#### 2.2 LDPC Code History

LDPC codes and their iterative decoding techniques were first proposed in Gallager's 1963 paper [22]. The computational requirements of the codes did not allow them to be implemented at the time (Gallager could only simulate low noise situations using small codeword lengths [22]) and LDPC codes were forgotten.

In 1993 Turbo codes were introduced by Berrou et al. [37]. Turbo codes utilise an iterative decoding method which relies heavily on APP obtained using the method proposed by Bahl et al. [38]. Turbo codes became widely adopted due to their ability to approach the Shannon channel capacity [2] which led to a surge in the research of iterative decoding techniques. In 1996 Gallager's paper [22] and LDPC codes were rediscovered by MacKay et al. [23].

Initially LDPC code performance lagged behind that of Turbo codes, but have recently surpassed them at higher code rates [3]. LDPC codes have since been adopted by many communications standards particularly in the video broadcast [41; 42; 43] and high speed Wi-Fi [44; 45; 47; 13; 46] domains.

#### 2.3 Iterative Codes and the Sum-Product Algorithm

This section discusses the SPA and its application in iterative decoding as used in LDPC codes. It provides a link between iterative and non-iterative decoding and is a summary of the work of Kschischang et al. [7].

The sum-product algorithm<sup>1</sup> is a general theory that allows calculation of marginal values in complex systems [7]. It is a generalisation of many popular probability inference algorithms in the fields of artificial intelligence, statistical modelling and digital communications [7]. Examples include the BCJR forward-backward algorithm [38], the Viterbi algorithm, Kalman filters and, more specifically for this paper, iterative decoding algorithms such as those used by Turbo codes and LDPC codes. Each of these examples employs some version of the sum-product algorithm [7].

The notation used will be similar to that of Kschischang et al. [7] for simplicity. Given a set of variables  $\mathbf{x} = \{x_1, ..., x_n\}$  which form part of some global function  $G(\mathbf{x})$ , then there exist *n* marginal functions  $G_i(x_i)$ . A marginal function is defined as

$$G_i(x_i) = \sum_{x_1} \dots \sum_{x_{i-1}} \sum_{x_{i+1}} \dots \sum_{x_n} G(\mathbf{x})$$

(2.3.1)

where  $\sum_{x_j} G(\mathbf{x})$  indicates summation over  $G(\mathbf{x})$  for all values of  $x_j$ . Note the absence of the variable  $x_i$  in the summations of (2.3.1). The marginal is computed by summing over all variations of the global function excluding the variable being marginalised. Such operations will be required often in this writing, and as such a short notation for it is presented as

$\overset{\sim i}{\underset{j}{\square}}$

$<sup>^{1}</sup>$ An alternative explanation using the distributive law is available in [26]. The sum-product approach is chosen here as it has closer ties to existing graphical models of LDPC codes.

which implies performing the operation  $\Box$  for all valid j values except i. (2.3.1) can then be simply rewritten as

$$G_i(x_i) = \sum_{x_j}^{\sim x_i} G(\mathbf{x}) \tag{2.3.2}$$

The purpose of the sum-product algorithm is to efficiently compute marginals, reusing partial sums where possible [7]. It does this by factorising the global function into smaller, local functions which can be represented accurately using a factor graph.

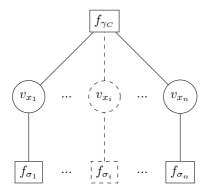

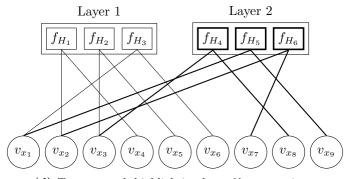

A factor graph is a bipartite graph in which one node set  $\mathbf{v} = \{v_{x_1}, ..., v_{x_n}\}$  represents the variables  $\{x_1, ..., x_n\}$  and the other node set  $\mathbf{f} = \{f_{g_1}, ..., f_{g_m}\}$  represents the factorised local functions  $\{g_1(\mathbf{x}_1), ..., g_m(\mathbf{x}_m)\}$  such that

$$G(\mathbf{x}) = \prod_{i} g_i(\mathbf{x}_i) \quad \mathbf{x}_i \subseteq \mathbf{x}$$

The factor graph of  $G(\mathbf{x})$  contains *n* variable nodes **v** and *m* function nodes **f**. An edge is formed between nodes  $v_{x_i}$  and  $f_{g_j}$  if  $x_i \in \mathbf{x}_j$  of the local factor function  $g_j(\mathbf{x}_j)$ .

The sum-product algorithm only gets exact marginals when applied on a cycle-free factor graph [7]. The next section discusses the execution of the sum-product algorithm on cycle-free graphs, followed by a discussion on graphs containing cycles.

#### 2.3.1 Acyclic Factor Graphs

If a graph is cycle free, every node has at most one path to any other node. This makes it trivial to transform the graph into a tree with an arbitrary node as the root node. A marginal  $G_i(x_i)$  is calculated by choosing variable node  $v_i$  to be the root node of the tree. Information is exchanged between nodes by passing messages along edges. A message from some node a to node b will be denoted by  $Q_{a-b}$ .

Computation starts in the leaf nodes where each variable leaf node passes an identity function message to its parent and each function leaf node passes a description of its function. Each internal node then waits for messages from all of its child nodes to arrive before computing the message to its parent. In such a manner, messages travel up the tree until they reach the root where the final marginal is computed. A variable node  $v_a$  computes the message to its parent function node  $f_b$  as the product of the messages received from its children i.e.

$$Q_{v_a - f_b} = \prod_{i}^{\sim b} Q_{f_i - v_a} \tag{2.3.3}$$

A function node  $f_b$  computes the message to its parent variable node  $v_a$  by executing its function on the messages received from its children and then marginalises out its parent variable using (2.3.2) i.e.

$$Q_{f_b - v_a} = \sum_{i}^{\sim a} g_b(Q_{v_i - f_b})$$

(2.3.4)

As one can see in (2.3.3) and (2.3.4), the sum-product algorithm was apply named after the only operations it requires, namely summation and multiplication. It is also possible to calculate (2.3.3) as

$$Q_{v_a - f_b} = Q_{f_k - v_a} \cdot \prod_{i}^{\sim b, k} Q_{f_i - v_a}$$

(2.3.5)

and (2.3.4) as

$$Q_{f_b - v_a} = Q_{v_k - f_b} + \sum_{i}^{\sim a, k} g_b(\mathbf{x}_b)$$

(2.3.6)

which shows the possibility of calculating (2.3.3) and (2.3.4) recursively as

$$\theta(Q_1, ..., Q_n) = \theta(Q_1, \theta(Q_2, ..., Q_n))$$

(2.3.7)

where  $\theta$  represents the relevant function.

In order to compute all n marginals it is possible to avoid repeating the full computations (and graph restructuring) by employing the full sum-product algorithm [7]. In this algorithm no node is chosen as the root but computation still begins at the leaf nodes. Each vertex now waits until it has received messages from all but one neighbour. It then forms a message in the same manner as before and sends it to this neighbour – essentially treating this neighbour as its parent. It then awaits a return message. Once received it can form messages to the rest of its neighbours, treating each as a parent node in turn. The algorithm terminates once messages have traversed an edge in both directions.

This algorithm works for any system in which multiplication and addition are well defined and the corresponding factor graph is cycle free. Here is an example taken from [27] to illustrate how the sum-product algorithm is expressed as the well known APP algorithm.

Given a sequence  $\mathbf{y} = \{y_1, ..., y_n\}$  received from a memoryless channel  $\sigma$ , the APP distribution  $G(\mathbf{x})$  for the original codeword symbols  $\mathbf{x} = \{x_1, ..., x_n\}$  of some code C is proportional to

$$G(\mathbf{x}) = \sigma_{\mathbf{y}}(\mathbf{x})p(\mathbf{x})$$

where  $\sigma_{\mathbf{y}}(\mathbf{x})$  is the channel conditional probability density function for a given  $\mathbf{y}$  and  $p(\mathbf{x})$  is the *a priori* probability distribution of  $\mathbf{x}$ . One can factorise  $\sigma_{\mathbf{y}}(\mathbf{x})$  as follows because the channel is memoryless:

$$\sigma_{\mathbf{y}}(\mathbf{x}) = \prod_{i} \sigma_i(x_i)$$

resulting in

$$G(\mathbf{x}) = p(\mathbf{x}) \prod_{i} \sigma_i(x_i)$$

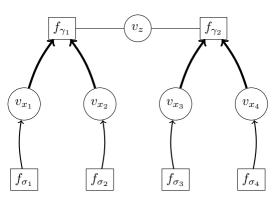

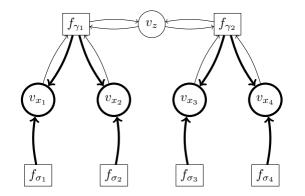

The factor graph for this general APP distribution function is show in figure 2.2.

If each codeword is equally likely then according to [7] the *a priori* probability distribution can be written as

$$p(\mathbf{x}) = \frac{1}{|C|} \gamma_C$$

where |C| is the number of codewords in C and  $\gamma_C$  the characteristic function of C. This characteristic function can often also be factorised.

Figure 2.2 – General APP factor graph.

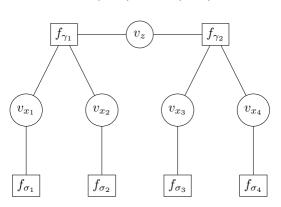

For a code, the characteristic function is simply an indicator function which indicates membership of the code set. For the following binary code

$$C = \{(0, 0, 0, 0), (0, 1, 1, 1), (1, 0, 1, 1), (1, 1, 0, 0)\}$$

the indicator function can be represented as

$$\gamma_C = [x_1 \oplus x_2 = x_3 = x_4]$$

where  $\mathbf{x} = \{x_1, x_2, x_3, x_4\}$  are the code bits and  $\oplus$  represents the logical XOR operation. This constraint can be split into two simpler functions by making use of an intermediary variable z such that

$$\gamma_1 = \begin{bmatrix} x_1 \oplus x_2 \oplus z = 0 \end{bmatrix}$$

$$\gamma_2 = \begin{bmatrix} x_3 = x_4 = z \end{bmatrix}$$

and

$$\gamma_C = \gamma_1 \cdot \gamma_2$$

The APP distribution function then becomes

$$G(\mathbf{x}) = \gamma_1 \cdot \gamma_2 \cdot \prod_i \sigma_i(x_i)$$

where the constant  $\frac{1}{|C|}$  has been dropped for simplicity. The factor graph representing this is shown in figure 2.3.

Messages in a soft decoding algorithm usually contain two pieces of information, namely the probability that some bit is a zero and the probability that it is a one. Let this information be represented as  $Q_{a-b}^0$  and  $Q_{a-b}^1$  respectively for some message  $Q_{a-b}$ .

To illustrate how the message passing works in practice, let the memoryless channel  $\sigma$  be a binary symmetric channel with crossover probability  $\varepsilon$  and the received codeword  $\mathbf{y} = \{0, 0, 1, 0\}$ . All messages will be sent as 2-tuples i.e.

$$Q_{a-b}^{\rm D} = (Q_{a-b}^{\rm 0} , Q_{a-b}^{\rm 1})$$

Important to note is that every internal variable node in this graph is of degree two. This implies that messages received on one edge can simply be sent out on the other edge with no computation required [7].

The characteristic sub-function nodes  $f_{\gamma_1}$  and  $f_{\gamma_2}$  operate as follows to marginalise out a variable q:

$$r = (a, b) \qquad s = (c, d)$$

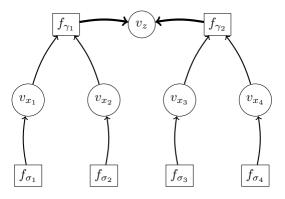

Figure 2.3 – APP example factor graph.

$$\sum_{i}^{\sim q} f_{\gamma_1}(q, r, s) = (a \cdot c + b \cdot d , a \cdot d + b \cdot c)$$

$$\sum_{i}^{\sim q} f_{\gamma_2}(q, r, s) = (a \cdot c , b \cdot d) \cdot \eta$$

where  $\eta$  is a normalising factor

$$\eta = \frac{1}{a \cdot c + b \cdot d}$$

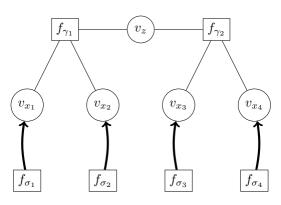

The algorithm starts in the leaf nodes, namely function nodes  $f_{\sigma_i}$ , which send messages  $Q_{f_{\sigma_i} - v_{x_i}}$  to the codeword symbol variable nodes  $v_{x_i}$ . For this example the messages would be

$$\begin{split} Q^{\mathrm{D}}_{f_{\sigma_1} \cdot v_{x_1}} &= (\mathrm{Pr}(x_1 = 0) \ , \ \mathrm{Pr}(x_1 = 1)) = (1 - \varepsilon \ , \ \varepsilon) \\ Q^{\mathrm{D}}_{f_{\sigma_2} \cdot v_{x_2}} &= (\mathrm{Pr}(x_2 = 0) \ , \ \mathrm{Pr}(x_2 = 1)) = (1 - \varepsilon \ , \ \varepsilon) \\ Q^{\mathrm{D}}_{f_{\sigma_3} \cdot v_{x_3}} &= (\mathrm{Pr}(x_3 = 0) \ , \ \mathrm{Pr}(x_3 = 1)) = (\varepsilon \ , \ 1 - \varepsilon) \\ Q^{\mathrm{D}}_{f_{\sigma_4} \cdot v_{x_4}} &= (\mathrm{Pr}(x_4 = 0) \ , \ \mathrm{Pr}(x_4 = 1)) = (1 - \varepsilon \ , \ \varepsilon) \end{split}$$

This allows the variable nodes  $v_{x_i}$  to compute their messages to their respective characteristic sub-function nodes  $f_{\gamma_1}$  and  $f_{\gamma_2}$  as

$$\begin{split} Q^{\mathrm{D}}_{v_{x_1}\text{-}f_{\gamma_1}} &= (1-\varepsilon \;,\; \varepsilon) \\ Q^{\mathrm{D}}_{v_{x_2}\text{-}f_{\gamma_1}} &= (1-\varepsilon \;,\; \varepsilon) \\ Q^{\mathrm{D}}_{v_{x_3}\text{-}f_{\gamma_2}} &= (\varepsilon \;,\; 1-\varepsilon) \\ Q^{\mathrm{D}}_{v_{x_4}\text{-}f_{\gamma_2}} &= (1-\varepsilon \;,\; \varepsilon) \end{split}$$

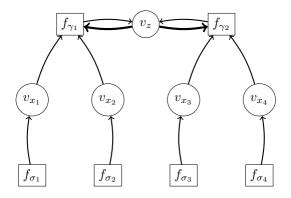

These characteristic sub-function nodes then calculate the marginal probabilities messages for variable node  $v_z$  as

$$Q_{f_{\gamma_1} \cdot v_z}^{\mathrm{D}} = \left( (1-\varepsilon)^2 + \varepsilon^2 , \ 2\varepsilon - 2\varepsilon^2 \right)$$

$$Q_{f_{\gamma_2} \cdot v_z}^{\mathrm{D}} = \left( (1-\varepsilon)^2 + \varepsilon^2 , \ (1-\varepsilon)^2 + \varepsilon^2 \right) \cdot \eta_A$$

$$\eta_A = \frac{1}{2(1-\varepsilon)^2 + 2\varepsilon^2}$$

Figure 2.4 – APP example: step 1.

$v_z$  can then immediately send these messages on to the other characteristic sub-function node  $f_{\gamma_2}$

$$Q_{v_z f_{\gamma_2}}^{\mathrm{D}} = Q_{f_{\gamma_1} v_z}^{\mathrm{D}}$$

$$= \left( (1 - \varepsilon)^2 + \varepsilon^2 , \ 2\varepsilon - 2\varepsilon^2 \right)$$

and  $f_{\gamma_1}$

$$Q_{v_z - f_{\gamma_1}}^{\mathrm{D}} = Q_{f_{\gamma_2} - v_z}^{\mathrm{D}}$$

=  $\left( (1 - \varepsilon)^2 + \varepsilon^2 , (1 - \varepsilon)^2 + \varepsilon^2 \right) \cdot \eta_A$

=  $(0.5, 0.5)$

The characteristic sub-function nodes can now compute their marginals for the variable

Figure 2.5 – APP example: step 2.

Figure 2.6 – APP example: step 3.

$\mathbf{13}$

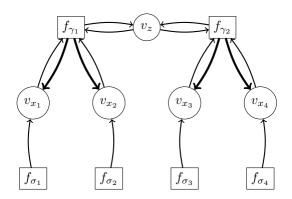

nodes  $v_{x_i}$

$$\begin{split} Q^{\mathrm{D}}_{f_{\gamma_1} \cdot v_{x_1}} &= (0.5 \cdot (1-\varepsilon) + 0.5 \cdot \varepsilon , \ 0.5 \cdot \varepsilon + 0.5 \cdot (1-\varepsilon)) \\ &= (0.5 , \ 0.5) \\ Q^{\mathrm{D}}_{f_{\gamma_1} \cdot v_{x_2}} &= (0.5 \cdot (1-\varepsilon) + 0.5 \cdot \varepsilon , \ 0.5 \cdot \varepsilon + 0.5 \cdot (1-\varepsilon)) \\ &= (0.5 , \ 0.5) \\ Q^{\mathrm{D}}_{f_{\gamma_2} \cdot v_{x_3}} &= \left( (1-\varepsilon) \cdot ((1-\varepsilon)^2 + \varepsilon^2) , \ \varepsilon \cdot (2\varepsilon - 2\varepsilon^2) \right) \cdot \eta_B \\ &= (1 - 3\varepsilon + 4\varepsilon^2 - 2\varepsilon^3 , \ 2\varepsilon^2 - 2\varepsilon^3) \cdot \eta_B \\ Q^{\mathrm{D}}_{f_{\gamma_2} \cdot v_{x_4}} &= \left( \varepsilon \cdot ((1-\varepsilon)^2 + \varepsilon^2) , \ (1-\varepsilon) \cdot (2\varepsilon - 2\varepsilon^2) \right) \cdot \eta_C \\ &= \left( \varepsilon - 2\varepsilon^2 + 2\varepsilon^3 , \ 2\varepsilon - 4\varepsilon^2 + 2\varepsilon^3 \right) \cdot \eta_C \\ \eta_B &= \frac{1}{1 - 3\varepsilon + 6\varepsilon^2 - 4\varepsilon^3} \\ \eta_C &= \frac{1}{2\varepsilon - 6\varepsilon^2 + 4\varepsilon^3} \end{split}$$

Technically, the algorithm continues by passing messages down to the channel conditional probability function nodes  $f_{\sigma_i}$ . This is not necessary in this specific case as these are static functions and cannot change, and also cannot pass messages on further. The APP for each bit  $x_i$  can now be computed as the product of all the received messages of variable node  $v_{x_i}$ .

Figure 2.7 – APP example: step 4.

Figure 2.8 - APP example: step 5.

Figure 2.9 – APP example: final calculations at variable nodes.

This gives the following un-normalised probabilities:

$$\begin{aligned} G_1(x_1) &= (0.5 \cdot (1-\varepsilon) , \ 0.5 \cdot \varepsilon) \\ G_2(x_2) &= (0.5 \cdot (1-\varepsilon) , \ 0.5 \cdot \varepsilon) \\ G_3(x_3) &= \left( (1-3\varepsilon + 4\varepsilon^2 - 2\varepsilon^3) \cdot \varepsilon , \ 2\varepsilon - 4\varepsilon^2 + 2\varepsilon^3 \cdot (1-\varepsilon) \right) \cdot \eta_B \\ G_4(x_4) &= \left( (\varepsilon - 2\varepsilon^2 + 2\varepsilon^3) \cdot (1-\varepsilon) , \ (2\varepsilon - 4\varepsilon^2 + 2\varepsilon^3) \cdot \varepsilon \right) \cdot \eta_C \\ \eta_B &= \frac{1}{1-3\varepsilon + 6\varepsilon^2 - 4\varepsilon^3} \\ \eta_C &= \frac{1}{2\varepsilon - 6\varepsilon^2 + 4\varepsilon^3} \end{aligned}$$

For a crossover probability of  $\varepsilon = 0.1$  the normalised APP are

$$G_1(x_1) = (0.9, 0.1)$$

$$G_2(x_2) = (0.9, 0.1)$$

$$G_3(x_3) = (0.82, 0.18)$$

$$G_4(x_4) = (0.82, 0.18)$$

#### 2.3.2 Cyclic Factor Graphs

The previous section explained the usage of the sum-product algorithm on graphs containing no cycles. The concept for graphs containing cycles and the message forming rules are the same, however the message passing changes to an iterative version. The issue with the cycle-free message passing algorithm is that nodes forming a cycle will never start passing messages. Each node in a cyclic sub-graph has two edges within the sub-graph. This means that every node in the sub-graph is waiting on messages from the other nodes resulting in a deadlock.

This issue is solved by assuming every node receives a unit message on each of its edges at the start of the algorithm [7], allowing every node to compute messages right from the start. If this is done in a cycle-free graph, the message passing will eventually come to a natural halt. In a graph with cycles the message passing never terminates naturally, as a message sent between two nodes in a cycle will propagate through the cycle until it reaches the original sender node, which prompts it to send a new message again, restarting the process. Message passing in cyclic graphs therefore needs some form of halt condition – usually until some maximum number of iterations has been reached or convergence has been determined.

As mentioned previously, the sum-product algorithm only calculates exact solutions when operating on cycle-free factor graphs. When executed iteratively, the sum-product algorithm produces approximate solutions [7]. Despite that, codes using the iterative algorithm such as LDPC and Turbo codes are capable of good error correcting performance. The exact reasons for this are the topic of much research currently [7]

#### 2.4 LDPC Decoding

In this section we delve into the inner workings of LDPC decoding. We start with the definition of an LDPC code and move on to its representation as a factor graph using the SPA. From there we derive the full LDPC decoding algorithm using the SPA as a starting point. We end off by showing how various approximations, message structuring and message schedules can be used to simplify the decoding process.

An LDPC code C is entirely defined by its binary parity matrix **H**. Such a matrix has dimensions  $(m \times n)$  i.e. it has m rows and n columns. Each row represents a parity equation and each column a codeword bit. The LDPC code C therefore has a codeword length of n and contains m parity equations. A parity equation ensures that either an odd (odd parity) or even (even parity) number of ones is present in the codeword bits that are participating in the equation. The parity chosen is irrelevant so long as one is consistent throughout. A codeword bit j participates in parity equation i if

$$H_{i,i} = 1$$

A codeword is only valid if it satisfies every parity equation in the parity matrix i.e. for even parity a codeword  $\mathbf{x}$  is valid if it satisfies

$$\mathbf{H} \cdot \boldsymbol{x}^T = \mathbf{0} \tag{2.4.1}$$

where the dot-product is binary i.e. using modulo 2. A code C is therefore made up of all codewords that satisfy (2.4.1).

These parity equations equate to the characteristic function for C which allows the calculation of the APP (if the channel model is memoryless) as

$$G(\mathbf{x}) = \frac{1}{|C|} \prod_{j} f_{\sigma_j}(x_j) \prod_{i} H_i(\mathbf{x}_i)$$

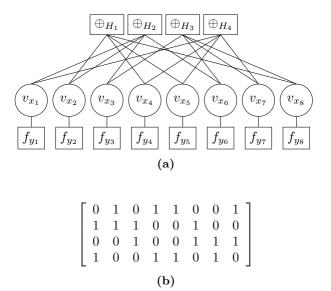

where  $\{H_1(\mathbf{x}_1), ..., H_m(\mathbf{x}_m)\}$  are the *m* parity equations of **H** and  $\mathbf{x}_i$  the subset of bit variables participating in parity equation  $H_i$ . This leads to factor graphs as seen in figure 2.10a, commonly referred to as Tanner graphs after Tanner [24] first proposed their use in LDPC codes. In Tanner graphs the only variables nodes are nodes representing the codeword bits,  $\mathbf{v}_{\mathbf{x}} = \{v_{x_1}, ..., v_{x_n}\}$ . Function nodes fall into exactly two types: conditional probability function nodes  $f_{\sigma} = \{f_{\sigma_1}, ..., f_{\sigma_n}\}$  (whose messages are constant during a decoding) and parity-check function nodes  $\mathbf{f}_{\mathbf{H}} = \{f_{H_1}, ..., f_{H_m}\}$ .

In the APP example of section 2.3.1, all variable nodes were of degree two. This allowed an incoming message on one edge to simply be sent out the other edge with no computation required. For variable nodes of a higher degree this is no longer possible and one needs to follow (2.3.3) to compute messages. For binary decoding this implies calculating the probability that a variable node is a zero or a one. A variable node  $v_z$  could compute the probability messages to function node  $f_j$  as

$$Q^0_{v_z - f_j} = \prod_i^{\sim j} Q^0_{f_i - v_j}$$

Figure 2.10 – A Tanner graph and its parity matrix.

and

$$Q^1_{v_z - f_j} = \prod_i^{\sim j} Q^1_{f_i - v_z}$$

Unfortunately, this allows for cases where  $Q_{v_z-f_j}^0 + Q_{v_z-f_j}^1 \neq 1$ , which would result in messages not being uniform. This is corrected by adding a normalising factor to ensure all messages have a probability magnitude of one i.e.

$$Q_{v_z - f_j}^0 = \frac{\prod_{i}^{j} Q_{f_i - v_z}^0}{\prod_{i}^{j} Q_{f_i - v_z}^0 + \prod_{i}^{j} Q_{f_i - v_z}^1}$$

(2.4.2)

and

$$Q_{v_z - f_j}^1 = \frac{\prod_{i=1}^{n} Q_{f_i - v_z}^1}{\prod_{i=1}^{n} Q_{f_i - v_z}^0 + \prod_{i=1}^{n} Q_{f_i - v_z}^1}$$

(2.4.3)

A parity-check function node was also dealt with in the APP example. It had a degree of three. The calculation of messages from a parity-check function node  $f_j$  of arbitrary degree to a variable node  $v_z$  can be generalised as

$$Q_{f_j - v_z}^0 = \frac{1}{2} + \frac{1}{2} \prod_{i=1}^{\infty z} \left( 1 - 2Q_{v_i - f_j}^1 \right)$$

(2.4.4)

and

$$Q_{f_j - v_z}^1 = \frac{1}{2} + \frac{1}{2} \prod_{i=1}^{n-2} \left( 1 - 2Q_{v_i - f_j}^0 \right)$$

(2.4.5)

These equations already result in normalised messages and stem from Gallager's original paper [22] on LDPC codes. He derived them using [22, Lemma 4.1] whereby the probability

$$\frac{1}{2} + \frac{1}{2} \prod_{i} (1 - 2\Pr(x_i = S))$$

In practice, a message format such as a 2-tuple requires calculating two separate messages – one for each probability (even if only one is sent; the one requires the other for normalisation), which is inefficient.

#### 2.4.1 LDPC Codes Message Formats

The necessity of sending two separate numbers per message can be avoided by using a likelihood ratio, defined as

$$Q_{a-b}^{\rm LR} = \frac{Q_{a-b}^0}{Q_{a-b}^1} \tag{2.4.6}$$

This allows the computation and sending of both message pieces as one number. Substituting (2.4.2) and (2.4.3) into (2.4.6), gives the following calculation for the messages from variable node z to function node j

$$Q_{v_z \cdot f_j}^{\text{LR}} = \frac{Q_{v_z \cdot f_j}^0}{Q_{v_z \cdot f_j}^1}$$

$$= \frac{\prod\limits_i^{j} Q_{f_i \cdot v_z}^0}{\prod\limits_i^{j} Q_{f_i \cdot v_z}^0 + \prod\limits_i^{j} Q_{f_i \cdot v_z}^1} \cdot \frac{\prod\limits_i^{j} Q_{f_i \cdot v_z}^0}{\prod\limits_i^{j} Q_{f_i \cdot v_z}^1}$$

$$= \frac{\prod\limits_i^{j} Q_{f_i \cdot v_z}^0}{\prod\limits_i^{j} Q_{f_i \cdot v_z}^1}$$

$$= \prod\limits_i^{\sim j} Q_{f_i \cdot v_z}^{\text{LR}}$$

$$(2.4.7)$$

where one can see that the normalisation factor cancels out. The message probability pieces  $Q_{a-b}^0$  and  $Q_{a-b}^1$  can be written in terms of the likelihood message  $Q_{a-b}^{LR}$  by using (2.4.6) and the fact that  $Q_{a-b}^0 + Q_{a-b}^1 = 1$ . This results in

$$Q_{a-b}^{0} = \frac{Q_{a-b}^{\text{LR}}}{Q_{a-b}^{\text{LR}} + 1}$$

(2.4.8)

and

$$Q_{a-b}^1 = \frac{1}{Q_{a-b}^{\text{LR}} + 1} \tag{2.4.9}$$

Substituting the parity-check message computation equations (2.4.4) and (2.4.5) into (2.4.6) gives

$$Q_{f_j \cdot v_z}^{\text{LR}} = \frac{1 + \prod\limits_{i}^{\sim z} \left(1 - 2Q_{v_i \cdot f_j}^1\right)}{1 + \prod\limits_{i}^{\sim z} \left(1 - 2Q_{v_i \cdot f_j}^0\right)}$$

where  $Q_{v_i - f_j}^0$  and  $Q_{v_i - f_j}^1$  can be replaced using (2.4.8) and (2.4.9). This gives

$$Q_{f_{j} \cdot v_{z}}^{\text{LR}} = \frac{1 + \prod_{i}^{\sim z} \left(1 - \frac{2}{Q_{v_{i} \cdot f_{j}}^{\text{LR}} + 1}\right)}{1 + \prod_{i}^{\sim z} \left(1 - \frac{2Q_{v_{i} \cdot f_{j}}^{\text{LR}} + 1}{Q_{v_{i} \cdot f_{j}}^{\text{LR}} + 1}\right)}$$

$$= \frac{1 + \prod_{i}^{\sim z} \frac{Q_{v_{i} \cdot f_{j}}^{\text{LR}} - 1}{Q_{v_{i} \cdot f_{j}}^{\text{LR}} + 1}}{1 - \prod_{i}^{\sim z} \frac{Q_{v_{i} \cdot f_{j}}^{\text{LR}} - 1}{Q_{v_{i} \cdot f_{j}}^{\text{LR}} + 1}}$$

(2.4.10)

The likelihood ratio suffers from an underflow problem when represented using a limited resolution, as probabilities can reach very small numbers. This problem is fixed by using the log-likelihood ratio (LLR) to convey messages from node a to b as

$$Q_{a-b}^{\text{LLR}} = \ln \frac{Q_{a-b}^0}{Q_{a-b}^1} = \ln Q_{a-b}^{\text{LR}}$$

(2.4.11)

This message format has further advantages, one of which is the ability to determine the most likely symbol of the bit by looking at the sign of the LLR. Another bonus is the computationally friendly variable node message calculation. For some variable node  $v_z$  to function node  $f_j$  the message calculation becomes

$$Q_{v_z,f_j}^{\text{LLR}} = \ln\left(\prod_{i}^{j} Q_{f_i,v_z}^{\text{LR}}\right)$$

$$= \sum_{i}^{j} \log\left(Q_{f_i,v_z}^{\text{LR}}\right)$$

$$= \sum_{i}^{j} Q_{f_i,v_z}^{\text{LLR}}$$

(2.4.12)

where multiplication has now become summation in the log domain. This is of great benefit in real world applications as summation is much cheaper to do computationally. In a similar fashion, the bit node marginal probability can be calculated as

$$Q_{v_z - f_{=}}^{\text{LLR}} \sum_{i} Q_{f_i - v_z}^{\text{LLR}}$$

(2.4.13)

On the parity-check node message calculation side, things become more complex. Rearranging (2.4.11) gives

$$Q_{a-b}^{\rm LR} = e^{Q_{a-b}^{\rm LLR}}$$

Substituting this into (2.4.10) gives the following equation for a message from  $f_j$  to  $v_z$

$$Q_{f_j \cdot v_z}^{\text{LLR}} = \ln \frac{1 + \prod\limits_{i=e}^{\sim z} \frac{Q_{v_i \cdot f_j}^{\text{LLR}} - 1}{Q_{v_i \cdot f_j + 1}}}{1 - \prod\limits_{i=e}^{\sim z} \frac{Q_{v_i \cdot f_j}^{\text{LLR}} - 1}{Q_{v_i \cdot f_j + 1}^{\text{LLR}}}}$$

This can be simplified using the definitions

$$\tanh\left(\frac{\zeta}{2}\right) = \frac{\mathrm{e}^{\zeta} - 1}{\mathrm{e}^{\zeta} + 1}$$

$2\tanh^{-1}(\zeta) = \ln \frac{1+\zeta}{1-\zeta}$

CHAPTER 2. LITERATURE REVIEW

to get

$$Q_{f_j \cdot v_z}^{\text{LLR}} = \ln \frac{1 + \prod_{i}^{\sim z} \tanh\left(\frac{Q_{v_i \cdot f_j}^{\text{LLR}}}{2}\right)}{1 - \prod_{i}^{\sim z} \tanh\left(\frac{Q_{v_i \cdot f_j}^{\text{LLR}}}{2}\right)}$$

$$= 2 \tanh^{-1}\left(\prod_{i}^{\sim z} \tanh\left(\frac{Q_{v_i \cdot f_j}^{\text{LLR}}}{2}\right)\right)$$

(2.4.14)

Both tanh and tanh<sup>-1</sup> are transcendental functions, requiring lookup tables when implemented in hardware, and cause significant computational delays in software implementations. This has led to a range of approximation alternatives being developed.

#### 2.4.2 Parity-Check Message Approximations

The simplest of the approximations is called the min-sum algorithm and suffers a 2 dB performance loss when compared to the full sum-product decoding [1]. The min-sum message computation is defined as

$$Q_{f_j - v_z}^{\text{LLR}} = \prod_{i}^{\sim z} \text{sgn}(Q_{v_i - f_j}^{\text{LLR}}) \cdot \min_{i}^{\sim z} |Q_{v_i - f_j}^{\text{LLR}}|$$

(2.4.15)

which is equal to the min-sum algorithm used in the Viterbi algorithm [3]. This can be derived by splitting (2.4.14) into smaller recursive pieces (we show this is possible in (2.3.7)) until the smallest piece requires only two messages,  $\Psi$  and  $\Omega$ :

$$2 \tanh^{-1} \left( \tanh\left(\frac{\Psi}{2}\right) \tanh\left(\frac{\Omega}{2}\right) \right)$$

$$= \ln \frac{1 + \tanh\left(\frac{\Psi}{2}\right) \tanh\left(\frac{\Omega}{2}\right)}{1 - \tanh\left(\frac{\Psi}{2}\right) \tanh\left(\frac{\Omega}{2}\right)}$$

$$= \ln \frac{\cosh\left(\frac{\Psi}{2}\right) \cosh\left(\frac{\Omega}{2}\right) + \sinh\left(\frac{\Psi}{2}\right) \sinh\left(\frac{\Omega}{2}\right)}{\cosh\left(\frac{\Psi}{2}\right) \cosh\left(\frac{\Omega}{2}\right) - \sinh\left(\frac{\Psi}{2}\right) \sinh\left(\frac{\Omega}{2}\right)}$$

Applying the identities

$$\cosh(x+y) = \cosh(x)\cosh(y) + \sinh(x)\sinh(y)$$

$$\cosh(x-y) = \cosh(x)\cosh(y) - \sinh(x)\sinh(y)$$

gives

$$\ln \frac{\cosh\left(\frac{\Psi+\Omega}{2}\right)}{\cosh\left(\frac{\Psi-\Omega}{2}\right)} = \ln \left(e^{\Psi+\Omega} + e^{-\Psi-\Omega}\right) - \ln \left(e^{\Psi-\Omega} + e^{-\Psi+\Omega}\right)$$

For  $|x| \gg 1$

$\mathbf{e}^x + \mathbf{e}^{-x} \approx \mathbf{e}^{|x|}$

which results in the approximation

$$\begin{split} \ln \frac{\cosh \left(\frac{\Psi + \Omega}{2}\right)}{\cosh \left(\frac{\Psi - \Omega}{2}\right)} &\approx \ln \left( e^{|\Psi + \Omega|} \right) - \ln \left( e^{|\Psi - \Omega|} \right) \\ &= |\Psi + \Omega| - |\Psi - \Omega| \\ &= \operatorname{sgn} \Psi \operatorname{sgn} \Omega \cdot \min(|\Psi|, |\Omega|) \end{split}$$

19

Finally, by noting that

$$\operatorname{sgn} \Phi \cdot \operatorname{sgn} (\operatorname{sgn} \Psi \cdot \operatorname{sgn} \Omega) = \operatorname{sgn} \Phi \cdot \operatorname{sgn} \Psi \cdot \operatorname{sgn} \Omega$$

$$\min(|\Phi|, \min(|\Psi|, |\Omega|)) = \min(|\Phi|, |\Psi|, |\Omega|)$$

allows the approximation of (2.4.14) as the min-sum computation by using the recursive nature shown in (2.3.7). The transcendental tanh function and its inverse have now been approximated using only the product of the signum and minimum functions, of which the former reduces to the XOR of the signum function.

A few enhancements to the min-sum algorithm exist. The performance loss of the min-sum algorithm can be largely negated by using a correction factor. The normalised min-sum algorithm does this by multiplying the min-sum result by a positive number smaller than one [1]. The offset min-sum algorithm replaces each incoming message magnitude  $|\Psi|$  at a parity-check node by  $\max(|\Psi| - \beta, 0)$  [1]. This effectively removes the influence of all messages whose magnitude is less than  $\beta$ . A review of the performance trade-offs is done in [28]. The two min-sum algorithm adaptions can also be combined. In their simplest form, both algorithms' correction factor is a constant, although ideally it would vary with both iteration and node. A few adaptive algorithms that do this have been proposed, an example of which is discussed in [29].

#### 2.4.3 LDPC Message Passing Algorithms

A message passing schedule is often used to add some order to the message passing. General schedule types include:

Flooding Every node sends a message along every edge at the same time.

**Serial** Nodes send messages along edges one at a time.

**Clumping** A combination of flooding and serial. Nodes are grouped together, each group then takes turns to pass messages using the flood schedule.

Flooding and serial are trivial types and are not discussed further. LDPC codes have a few ways in which to take advantage of a clumping type schedule.

The standard LDPC message passing algorithm is called two phase message passing [1]. It splits the nodes into two clumps according to their type, namely variable nodes and function nodes. In one phase variable nodes receive messages and calculate their messages to the function nodes. This is known as the variable node update phase. In the other phase, function nodes receive messages and calculate their messages to the variable nodes. This is known as the check update phase, as the channel conditional function nodes don't require receiving messages or any calculation (their messages are a constant).

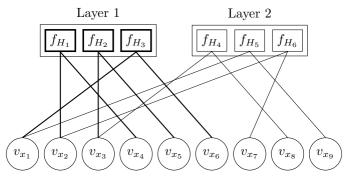

An extension of the two phase message passing is the layered decoding algorithm [1]. Messages are still passed during variable update and the check update phases. The parity-check function nodes are separated into groups called layers such that every variable node has at most one connection to each layer. During the check update phase only one layer updates its messages, the rest of the groups still pass the old messages. Variable nodes therefore receive at most one new message from parity-check nodes per variable update phase. This allows for simplification of the variable update phase's message calculation. It can also be used to unify the variable and check update phases as described in [1].

#### 2.5 General LDPC Encoding

LDPC codes need long codewords to reach good error correcting performance [23]. This makes encoding complexity with respect to code length an important factor. Unfortunately the encoding of an LDPC code is, in general, quadratic with code length. This can be demonstrated by splitting a codeword  $\mathbf{x}$  and the parity-check matrix  $\mathbf{H}$  into two parts such that

$$\mathbf{H} \cdot \mathbf{x}^{T} = \mathbf{0}^{T}$$

$$[\mathbf{H}_{i} | \mathbf{H}_{p}] \cdot \begin{bmatrix} \mathbf{x}_{i}^{T} \\ \mathbf{x}^{T} \end{bmatrix} = \mathbf{0}^{T}$$

(2.5.1)

becomes

where

$$\mathbf{x}_i$$

and  $\mathbf{x}_p$  are vectors containing the information bits and parity bits respectively. As

the information bits are already known, all that is required is to calculate the values for the

parity bits. This can be done by rearranging (2.5.1) to get

$$\mathbf{x}_p = \mathbf{H}_p^{-1} \, \cdot \, \mathbf{H}_i \, \cdot \, \mathbf{x}_i$$

Both parts of the parity matrix,  $\mathbf{H}_p$  and  $\mathbf{H}_i$ , are sparse because  $\mathbf{H}$  is sparse. This means that the dot product  $\mathbf{H}_i \cdot \mathbf{x}_i$  has linear complexity as the sparseness of  $\mathbf{H}_i$  can be exploited. Although  $\mathbf{H}_p$  is sparse, this does not mean  $\mathbf{H}_p^{-1}$  is, which results in quadratic complexity overall.

This encoding complexity has a few solutions, some of which are now examined.

#### 2.5.1 Lookup Table

All encoding can be relegated to performing a simple lookup in a table storing all possible information to codeword combinations. Due to the large code length requirements of LDPC codes, this implementation requires large volumes of memory. It is hardly ever used in practice but should be kept in mind as the cost of memory falls.

#### 2.5.2 Triangular Parity-Check Matrix

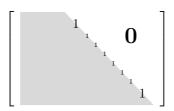

If the parity-check matrix can be transformed into a triangular matrix using only row and column operations then it is linearly encodable [3]. For an  $(m \times n)$  upper-triangular parity-check matrix, set the first n - m bits as information bits. This allows the calculation of the m parity bits in order by using the parity equations from top to bottom as each equation relies only on information bits and calculated parity bits.

This encoding method can also be expressed using a binary erasure channel decoder as described in [3]. After setting the n information bits and the parity bits as erased bits, the decoder will find the codeword in m iterations. This allows encoder and decoder to share chip real estate which is useful for transceiver and half-duplex systems [3].

Figure 2.11 – Parity matrix in upper-triangular form.

#### 2.5.3 Approximate Triangular Parity-Check Matrix

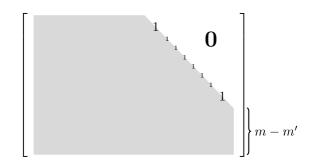

Richardson et al. [4] proposed transforming a parity-check matrix as close to a triangular matrix as possible. If a parity matrix can be transformed such that only m' rows do not fall into the triangular matrix form then m-m' parity bits can be calculated using the triangular matrix approach and the other m' parity bit values need to be calculated by solving the remaining m' parity-check equations. This last part has exponential complexity with respect to m'. Richardson et al. [4] show that for randomly constructed LDPC matrices,  $m' \ll m$  which allows encoding complexity to be linear with respect to overall code length in most cases.

Figure 2.12 – Parity matrix in approximate upper-triangular form.

#### 2.5.4 Block-Triangular parity-check Matrix